Basic HTML Version

489

'"

RIO

Rl8

Rl7

".

TPO

BUS 412

A'33ICl1~

I

774LSIO

'" p.

COlO A4 "~

~~:

oRt:'O ~::~

~Dl

AODRESS R / W 16

" ffi

CS~'

III

A~

C~.

14

A14

"

"

Gy"'r- ~""

-

~\:IIC"Cl1

••2'

E~,,-,

-41l-+-------""4--+

~

14(',1'1

CMOS RAM •

He

OSI

DIP SWITCHES

IN414~1I;

~

01

.~

01.

,

01>

,~

D"

~~

J

011

010

,

D.

a

1

~

ACe

cs a

IN4148

_0'

08

07

,~

D.

O.

.~

D.

e

O.

O.

01

I

~

R~

"

co •••.

c.

"qb~~O

.01*

I.

"

4.1K ENABLE

vc

0/'

~ SWITCH

LEfl.:.~

Rl1

'IE

I~=

'00

2. R01

RO'~

L~1 R12

~~:~fz~ :~~

5 RDz

f'Ol~

I~

"-J

100

, ee

oe

9

~"

'"'

B3

rm------

•

IC7

He

410

pm

~

-G2:::D

I

r-------------~------1_+_~_+~~1_-~.~7.~-~

•

IC29

DIP

RE:$ISTORS

N,.,.,.IIl_OGlG

of".,. ••. .,. ot.,.,.,

If')

(J(JUUUUUU

41_------------+h-----~++_+_H_+~----;·i;\7;;.3--<::IJ1-6

3

.7.

IJl'-5 4

Cll-

Vee

o~

~tf-

ICG

,I.

4 TO 113

41~~~@~~

DECODE. 5

741~4 6 7

" "

,00

~A

lOll

r----¥.e

111

/i."!

rfo

g

:i§==

L__L___+1_+-~-~-----;i;\;;.-~-·'_{'J6-~

'<If.+-

J6-~ '3

015p1-

R80 ~

10

12181'3

RBI

~11

r-----+++_+_~_+~----;w;-------(

IJ7-4

5

.7.

'Jr-;, 5

.77

.78

L----+1_1--<H------;·,,8;;.'-------(

IJij-5 12

~

'87

~A2

.88

~B2

R~'

'"

lJ~-7)

C2

~

•• 0

I-

IJ5-5

0'

"

,.,

~Al

0

0

.9.

o

IJ

~-!.

e,

00

~

~CI

'94

8 :::

o

0:'"

1-1-

U)~

>-1-

""

-'0

..

U)

0;

'I'

4 IC12 6

~

c~d

C37'n

.01*

•••

~ 14

12

."

"~

7.1;LS02 r

C.~+

j

•••

o,~

'"

10~

TPI

r<lLs~i'

L--------~++_+_~-++_+_f_--:i.i.<.--_(

IJ5-1

01

'"

"

~I~1~1~1 ;1~1~1

eI

"~'i,,

017

1

IN<ll<18

TP7

CMOS

~~t.I

,.,

6.8">1

ilENER

."

r"

'47

",

".<

R26

:3

9">1

lK

HNEFI

•

••

~R'8

R40

'"

P.7

2N4401

+

C23

'00

C24

.t

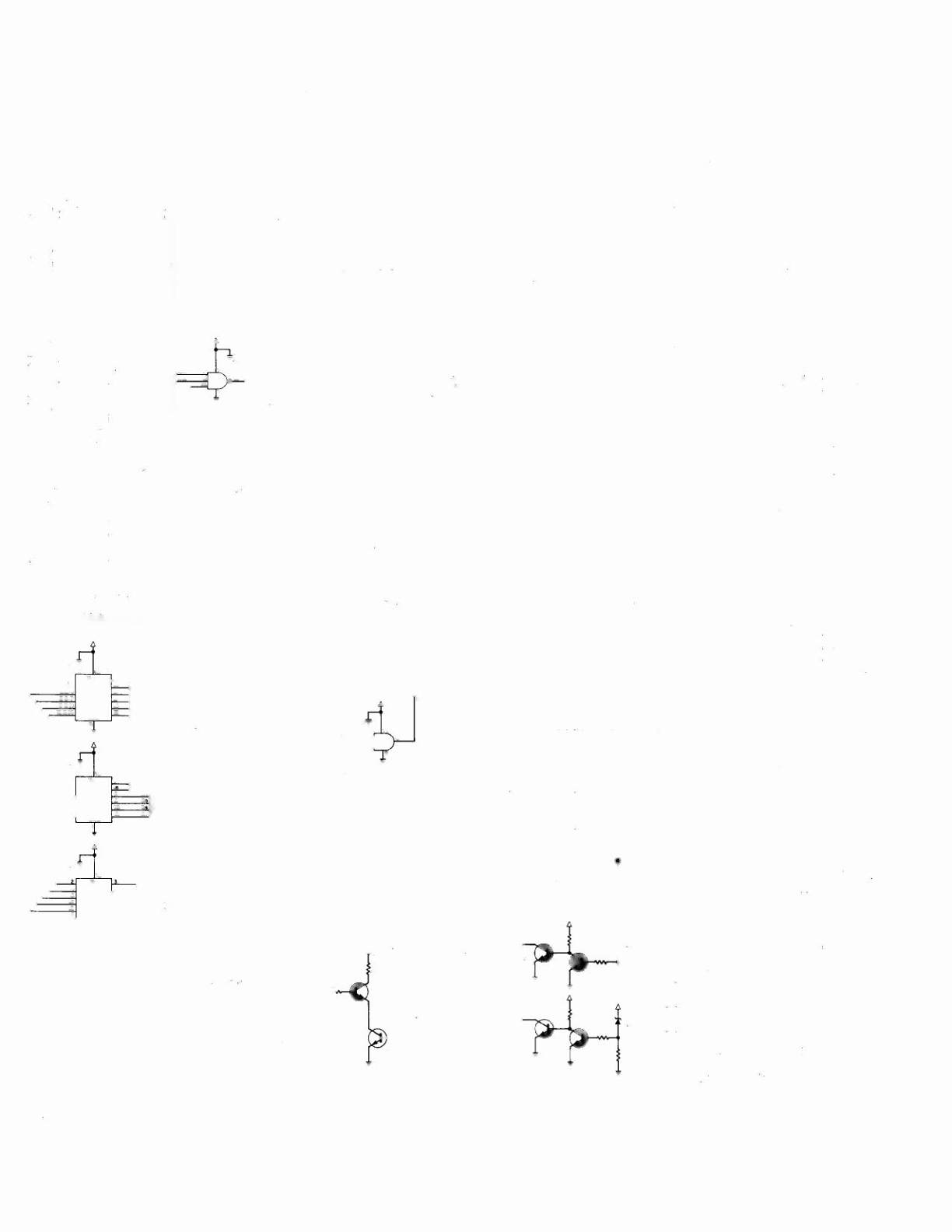

CPU Board Logic Diagram

3